# Схемотехнические методы повышения надежности операционных усилителей с предельным быстродействием в режиме большого сигнала

Н.Н. Прокопенко, А.С. Будяков, Н.В. Ковбасюк

Проблемная лаборатория перспективных технологий и процессов Центра исследования проблем безопасности РАН и ЮРГУЭС, НТЦ «МикАн», prokopenko@sssu.ru

Аннотация — Показано, что для повышения надежности операционных усилителей (ОУ) с предельным быстродействием в режиме большого сигнала необходимо вводить специальные ограничители уровня выходного тока их входных каскадов. Рассматриваются принципы построения архитектуры таких ОУ.

### І. Введение

Максимальная скорость нарастания выходного напряжения ( $\theta_{вых}$ ) операционных усилителей с классической архитектурой в режиме большого сигнала оценивается по формуле [1]

$$\vartheta_{\text{BMX}} = 2\pi f_1 U_{\text{FD}}, \qquad (1)$$

где  $f_1$  - частота единичного усиления ОУ;

$U_{rp}$  - напряжение ограничения входного каскада ОУ [1] (ВК).

Типичные значения  $U_{rp}$  типовых дифференциальных усилителей (BK) на биполярных транзисторах  $U_{rp}\approx U_{rp}^*=50$  мВ [1], [2], а малосигнальная крутизна их проходной характеристики  $y_{21}$  имеет достаточно большое значение  $y_{21}=I_{max}/U_{rp}^*$ , где  $I_{max}$  - максимальный выходной ток классического входного каскада, зависящий от тока общей эмиттерной цепи  $I_0$  [1]. В большинстве случаев  $I_{max}\approx I_0$ .

Из (1) следует, что для повышения  $\vartheta_{\text{вых}}$  необходимо схемотехническим путем увеличивать  $U_{\text{гр}} >> U_{\text{гр}}^*$ , т.е. обеспечивать линейный режим работы входного каскада во всем диапазоне импульсного изменения входного напряжения ОУ  $u_c$ , которое может достигать величины  $U_c \approx E^{(+)} = E^{(-)} = E_{\pi}$ , где  $E_{\pi}$  - напряжение питания. Обычно «продление» проходной характеристики ВК при сохранении ее наклона обеспечивается за счет цепей нелинейной коррекции [2] или специальной архитектуры ВК [4], [5].

Устойчивость ОУ с  $U_{rp} >> U_{rp}^*$  не ухудшится, если на большом сигнале будет выполняться равенство:

$$\frac{I_0}{U_{rp}^*} = \frac{I_{max}^*}{E_{rr}},$$

(2)

где  $I_{max}^*$  - максимальный выходной ток входного каскада, имеющего  $U_{rp} >> U_{rp}^*$  .

Следовательно,  $I_{max}^*$  в ОУ с предельным быстродействием может достигать величины

$$I_{\text{max}}^* = \frac{E_{\Pi}}{U_{\text{rp}}^*} I_0 >> I_0.$$

(3)

Таким образом, транзисторы входного каскада любого быстродействующего ОУ должны обеспечивать на время фронта переходного процесса  $t_{\varphi}$  выходной ток  $I_{max}^*$ , измеряемый десятками - сотнями миллиампер.

## II. Энергетические и токовые ограничения для входных каскадов

Следует ожидать, что полученный выше вывод потребует пересмотра сложившихся представлений о том, что входной каскад ОУ - это всегда микрорежимная подсхема. Если требуется получить предельно высокое быстродействие, то придется мириться с тем фактом, что выходной ток ВК должен (на короткое время) измеряться десятками, а иногда и сотнями миллиампер (3). Это первая проблема, которая не всегда учитывается при проектировании быстродействующих ОУ.

Вторая проблема связана с тем, что любой ОУ, работающий в структуре сложных аналоговоцифровых устройств, может (в нетиповых режимах) на достаточно большое время  $t_p >> t_{\varphi}$  перегружаться по входу большими сигналами (например, при включении питания). В этом случае на достаточно большое время  $t_p >> t_{\varphi}$  ко входам ОУ будут прикладываться напряжения, близкие к напряжению

питания, и поэтому большой выходной ток ВК может вызвать тепловое разрушение токоведущих дорожек, перегрев и выход из строя транзисторов микросхемы.

Таким образом, ОУ с предельным быстродействием при отсутствии защиты от чрезмерно больших статических выходных токов входного каскада не могут иметь высокую надежность.

Если исходить из энергетических ограничений, т.е считать, что входной каскад ОУ не выйдет из строя из-за перегрева элементов при длительной перегрузке по входу, то тогда становится заданной величина его максимального выходного тока и крутизна проходной характеристики для большого сигнала

$$y_{21}^* \approx \frac{I_{\text{max}}^*}{E_{\Pi}} \approx \frac{P_{K}}{E_{\Pi}^2},$$

(4)

где  $P_{\kappa}$  — допустимая мощность, рассеиваемая в элементах входного каскада его выходным током  $i_{c\kappa}$  за время перегрузки  $t_{p}$ , причем

$$P_{K} \approx \frac{E_{\pi}}{t_{p}} \int_{0}^{t_{p}} i_{cK} dt.$$

(5)

Таким образом, крутизна  $y_{21}^*$  входного каскада быстродействующего ОУ (наклон его проходной характеристики при  $u_{BX} >> U_{rp}^*$ ) не может выбираться без учета тепловых эффектов в микросхеме. Однако малосигнальный параметр  $y_{21}$  ВК, связанный с  $y_{21}^* \approx y_{21}$ , оказывает существенное влияние на многие динамические параметры ОУ [1], [2], в том числе малосигнальную частоту единичного усиления ОУ:

$$\omega_1 = \frac{y_{21}}{C_{\kappa}}, \tag{6}$$

где  $C_{\kappa}$  - емкость корректирующего конденсатора ОУ на выходе входного каскада;

Поэтому при рассматриваемых ограничениях частота единичного усиления надежного быстродействующего ОУ не может превышать величину

$$\omega_1 \le \omega_{\text{max}} = \frac{P_{\kappa}}{C_{\kappa} E_{\pi}^2} \,. \tag{7}$$

Последняя формула показывает, что для увеличения  $\omega_{max}$  следует увеличивать  $P_{\kappa}$ . При  $P_{\kappa}=$  const и  $y_{21}=$  const основной путь увеличения  $\omega_{1}$  и  $\vartheta_{выx}$  - это снижение емкости корректирующего конденсатора  $C_{\kappa}$ . Однако это достаточно сложная проблема, связанная с уменьшением абсолютных значений высокочастотных постоянных времени и их числа у

входного и выходного каскадов ОУ, элементов обратной связи, нагрузки. В конечном итоге  $C_{\kappa}$  определяется, в основном, достижениями технологии — высокочастотными параметрами интегральных транзисторов, емкостями на подложку, емкостями коллектор-база транзисторов и т.д.

Если предположить, что архитектура ОУ реализована по традиционным схемам на основе двухтактных повторителей тока или двухтактных «перегнутых» каскодов [1], [2], то минимально возможное значение  $C_{\kappa}$  определяется емкостями «коллектор — подложка»  $(C_{\pi})$  двух транзисторов, обеспечивающих перезаряд емкости  $C_{\kappa}$ , а также входной емкостью буферного усилителя БУ  $(C_{\text{БУ}})$

$$C_{K,min} \approx 2C_{\Pi} + C_{BY}$$

. (8)

Таким образом, наилучшее значение частоты единичного усиления ОУ с предельным быстродействием

$$\omega_1 \le \frac{P_K}{E_{\pi}^2 (2C_{\pi} + C_{\text{BY}})},$$

(9)

или

$$\omega_1 \le \frac{I_{\text{max}}^*}{E_{\Pi}(2C_{\Pi} + C_{\text{BY}})} \approx \frac{I_0}{U_{\text{pp}}^*(2C_{\Pi} + C_{\text{BY}})}.$$

(10)

Причем, максимальная скорость нарастания выходного напряжения ОУ

$$\theta_{\text{BbIX}} \le \frac{I_{\text{max}}^*}{(2C_{\Pi} + C_{\text{BY}})} = \frac{P_{K}}{E_{\Pi}(2C_{\Pi} + C_{\text{BY}})}.$$

(11)

Из уравнения (11) следует, что физическими ограничениями на максимальную скорость нарастания выходного напряжения ОУ с предельным значением  $\vartheta_{\rm Bыx}$  [1]-[4] и входными сигналами с амплитудой, близкой к напряжению питания, являются емкости на подложку транзисторов ВК и допустимая мощность, рассеиваемая на элементах его квазилинейного входного каскада при перегрузке  $(P_{\kappa})$ . Заметим, что данный вывод сделан при отсутствии защит по току у входного каскада и диапазоне его активной работы, близком к  $E_{\pi}$ .

Таким образом, разработчикам быстродействующих аналоговых микросхем (AM) приходится искать компромисс между надежностью работы AM в любых режимах (обрыв обратной связи, кратковременное отключение одного из источников питания, работа ОУ в режиме компаратора сигналов и т.д.) и предельным быстродействием.

Необходимо заметить, что традиционные ограничители входного напряжения ОУ [1] защищают его входные транзисторы от пробоя эмиттерно-базового p-n перехода, но ограничивают диапазон изменения входных сигналов на уровне  $U_{\text{огр}}{\approx}0,6\text{-}0,7B$ . Это не позволяет получить высокое

быстродействие, соизмеримое с быстродействием ОУ для линейного режима, так как в этом случае

$$\vartheta_{\text{BMX}}^* \approx 2\pi f_1 U_{\text{orp}} \le 1,4\pi f_1 [B/c].$$

# III. Способы построения цепей ограничения выходного тока входных каскадов

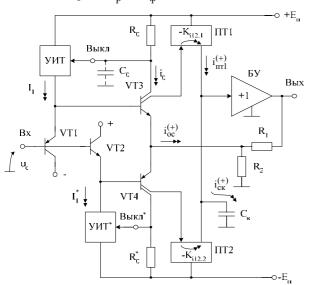

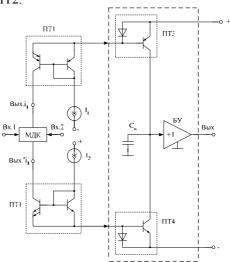

На рис. 1 представлена архитектура быстродействующего ОУ, особенность которой состоит в создании «интеллектуальной» защиты входного каскада, которая не влияет на работу схемы во время фронта переходного процесса  $t_{\varphi}$ , но ограничивает выходные токи входного каскада в том случае, если напряжение на входе ОУ действует длительное время  $t_{\varphi} >> t_{\varphi}$ .

Рис. 1. Способ ограничения максимального выходного тока ВК на «бриллиантовом транзисторе»

Операционный усилитель с токовой обратной связью (рис. 1) содержит входной каскад (VT1-VT4) с большими значениями максимального выходного тока

$$I_{\kappa 3.\text{max}} \approx \frac{\beta_3 I_1}{2}, \tag{12}$$

где  $\beta_3$  - коэффициент усиления по току базы двухколлекторного транзистора VT3;

$I_1$  - статическое значение выходного тока управляемого (по входу «Выкл») источника опорного тока  $I_1$ .

Условие (12) выполняется, если входной сигнал достаточно большой:  $U_{c.max} \ge \beta_3 I_1 \cdot R_1 \| R_2$  .

В схеме рис. 1 предусмотрена нелинейная отрицательная обратная связь, которая запирает источник опорного тока УИТ, если ток в

измерительном резисторе  $R_0$  превышает заданное значение  $I_{\rm orp}$ . При этом  $I_1$  уменьшается, что ограничивает выходной ток входного каскада на заданном уровне  $I_{\rm orp} < I_{\rm K3.max}$ . Как следствие максимальная скорость нарастания выходного напряжения ОУ с таким ВК (при  $C_0=0$ ) меньше предельно возможной и определяется по формуле

$$\theta_{\text{BMX}}^* \approx 2\pi f_1 I_{\text{OPD}} R_1 \| R_2$$

(15)

Регулировка инерционности петли ограничения выходного тока BK обеспечивается конденсатором  $C_0$ . Он может выбираться таким образом, чтобы защита по току не работала во время фронта входного импульсного сигнала, а ее включение происходило при  $t_p >> t_{\varphi}$ , т.е. когда в схеме ОУ возникают существенно-нелинейные режимы работы и возможен перегрев кристалла. В этом случае обеспечиваются предельные значения  $\vartheta_{\text{вых}}$ .

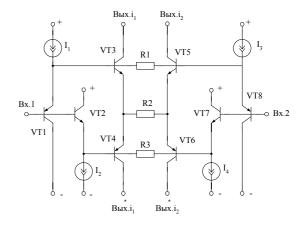

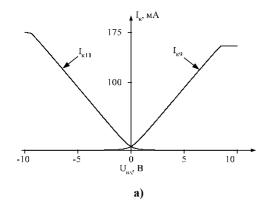

Управление величиной максимального выходного тока ВК быстродействующего ОУ, реализованного на мостовых дифференциальных усилителях типа quad-core [4] (рис. 2), может осуществляться либо за счет соответствующего выбора сомножителей произведения  $I_1\beta_3$  ( $I_2\beta_4$ ), либо путем введения специальных токоограничивающих резисторов  $R_1=R_3>>R_2$ .

Рис. 2. Способ ограничения выходного тока мостового ВК типа «quad-core»

В данной схеме напряжение ограничения входного каскада зависит от произведения

$$U_{rp} \approx R_1 I_1 = R_3 I_2$$

. (13)

В то же время крутизна проходной характеристики ВК на малом и большом сигналах, а также частота единичного усиления ОУ практически не зависят от  $R_1$ ,  $R_3$  и определяются резистором  $R_2$ :

$$y_{21} \approx R_2^{-1},$$

$$\omega_1 \approx \frac{1}{R_2 C_r},$$

(14)

где  $C_{\kappa}$  - емкость однополюсной коррекции ОУ.

Поэтому максимальная скорость нарастания выходного напряжения ОУ с входным каскадом «quad-core» для разных полярностей  $u_{\text{вых}}$  регулируется разными резисторами  $R_1$  и  $R_3$ :

$$\vartheta_{\text{BbIX}}^{*(+)} \approx \frac{R_1}{R_2} \frac{I_1}{C_K}, \ \vartheta_{\text{BbIX}}^{*(-)} \approx \frac{R_3}{R_2} \frac{I_2}{C_K}.$$

(15)

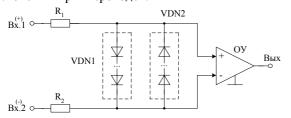

Включение нелинейного делителя напряжения «VDN1-R<sub>1</sub>-R<sub>2</sub>» на входе ОУ (рис. 3), имеющего входной каскад с расширенным диапазоном активной работы [1-4], также позволяет установить заданное значение  $U_{rp} = nU_{96} >> U_{rp}^*$  и, следовательно, максимальный выходной ток

$$I_{\text{max}}^* = I_0 \frac{nU_{36}}{U_{rp}^*}, \qquad (16)$$

и заданную максимальную скорость нарастания выходного напряжения

$$\vartheta_{\text{BMX}}^* \approx 2\pi f_1 \text{nU}_{96}, \qquad (17)$$

где  $U_{96} \approx 0.7 \; B;$  n - число последовательно включенных p-n переходов.

Рис. 3. Нелинейный ограничитель входного напряжения

Однако, шумы и дополнительная входная емкость p-n переходов VDN1-VDN2 не позволяет рекомендовать данную схему для широкого применения.

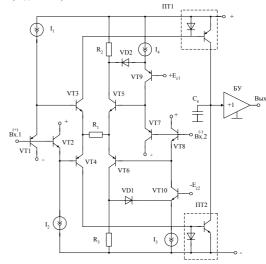

В связи с тем, что мостовой входной каскад рис. 2 является основой построения большинства быстродействующих операционных усилителей ведущих микроэлектронных фирм, следует рассмотреть другие варианты ограничения его выходного тока.

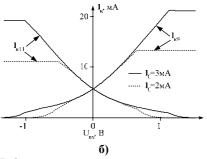

В схеме рис. 4 ограничители максимального тока транзисторов VT3, VT4 выполнены на элементах  $R_2$ , VD2 ( $R_3$ , VD1).

Рис. 4. Токовая защита в мостовом входном каскаде

Как только коллекторный ток транзистора VT5 ( $I_{\kappa 5}$ ) достигает заданного значения

$$I_{\text{orp}} \approx \frac{E_{\text{cl}}}{R_2},$$

(18)

начинает запираться транзистор VT9, что предотвращает дальнейшее увеличение  $I_{\kappa 5}$ . Поэтому в таком ОУ максимальная скорость нарастания выходного напряжения

$$\theta_{\text{Bbix}}^* \approx 2\pi f_1 \frac{R_1}{R_2} E_{cl} \approx \frac{E_{cl}}{R_2 C_{\kappa}} < \frac{\beta_3 I_1}{C_{\kappa}}.$$

(19)

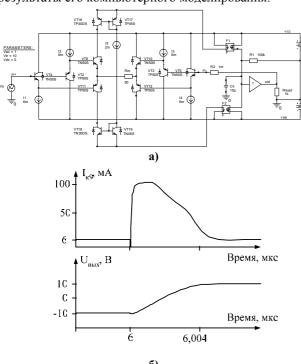

Ограничитель выходного тока мостового дифференциального каскада МДК в операционном усилителе рис. 5 реализован на основе токовых зеркал ПТ1, ПТ2.

Рис. 5. Архитектура операционного усилителя с ограничением максимальных токов входного каскада

Заданный уровень максимальных выходных токов МДК в статическом режиме  $I_{\text{огр}}$  устанавливается двухполюсниками  $I_1$  и  $I_2$ , а также соотношением площадей эмиттерных p-n переходов транзисторов, входящих в подсхему ПТ1, ПТ2.

При нулевом входном сигнале ОУ транзисторы подсхем ПТ1, ПТ2 находятся в насыщенном состоянии. Во время фронта переходного процесса ПТ1, ПТ2 не влияют на работу схемы ОУ. Как только медленно изменяющийся выходной ток МДК превысит заданное значение  $I_{\rm orp}$ , токовое зеркало ПТ1 (ПТ2) обеспечит его ограничение.

На рис. 6 показан операционный усилитель с рассматриваемой архитектурой, а на рис. 7 - результаты его компьютерного моделирования.

Рис. 6. Операционный усилитель рис. 5 в среде рярісе на моделях транзисторов ФГУП НПП "Пульсар" (а) и его переходные процессы (б)

Рис. 7. Статические проходные характеристики входного каскада ОУ без ограничения (а) и с ограничением (б) выходного тока

### VI. ЗАКЛЮЧЕНИЕ

- 1. При проектировании ОУ с предельно возможным быстродействием необходимо обращать внимание на энергетику не только выходных, но и входных каскадов, а также применять специальные цепи защиты, ограничивающие на заданном уровне максимальный ток входных каскадов во время фронта переходного процесса.

- 2. Предельно возможная скорость нарастания выходного напряжения быстродействующих ОУ определяется, с одной стороны, допустимой мощностью, рассеиваемой в элементах входного каскада во время его динамической перегрузки большим сигналом, а с другой суммарной емкостью на подложку транзисторов промежуточного каскада с высоким импедансом.

- 3. Разработчикам быстродействующих аналоговых микросхем (АМ) приходится искать компромисс между надежностью работы АМ в любых режимах (обрыв обратной связи, кратковременное отключение одного из источников питания, работа ОУ в режиме компаратора сигналов и т.д.) и предельным быстродействием.

- 4. Введение «интеллектуальных цепей» защиты по выходному току входных каскадов ОУ повышает их надежность при длительных перегрузках по входу.

### Литература

- [1] Операционные усилители с непосредственной связью каскадов / Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М. Л., 1979. 148 с.

- [2] Прокопенко Н.Н. Нелинейная активная коррекция в прецизионных аналоговых микросхемах / Н.Н.Прокопенко. Ростов-на-Дону: Изд-во СКНЦ ВШ, 2000. 222 с.

- [3] R.Widlar. Wide range operational amplifier input stage. US Patent № 4.797.629, 1989.

- [4] F.Moraveji. Fast clewing Amplifier using dinamic current mirrors. US Patent № 5.510.754, 1996.

- [5] Прокопенко Н.Н., Будяков А.С., Крюков С.В. Быстродействующий операционный усилитель. Заявка на патент № 2006105298 от 20.02.2006 г.